# SystemVerilog 3.0

# Accellera's Extensions to Verilog<sup>®</sup>

Editor's note:

Draft 5 reflects all changes approved in the HDL++ meetings 16 through 19 (through March 18, 2002)

Legend:

red strike through text indicates text to be deleted

- blue text indicates text that was added

-red text indicates editor notes or things we need to consider at a future meeting

- All strike through text in draft 4 has been deleted. Any strike through text in this draft are for text in draft 4 that has been approved for deletion.

- All new (in blue) text in draft 4 has been changed to regular text. Any text in blue in this draft is new text added since draft 4.

Sponsor

Accellera

**Abstract:** a set of extensions to the IEEE 1364-2001 Verilog Hardware Description Language to aid the creation and verification of abstract architectural level models

Copyright © 2002 by Accellera 1370 Trancas Street #163 Napa, CA 94558 Phone: (707) 251-9977 Fax: (707) 251-9877

This is an unapproved draft of a proposed Accellera Standard, subject to change. Use of information contained in the unapproved draft is at your own risk.

Do not copy, fax, reproduce, or distribute without written permission.

# **Table of Contents**

| Section | 1 Introduction to SystemVerilog                    | •••••• |

|---------|----------------------------------------------------|--------|

| Section | 2 Lexical Conventions Literal Values               | •••••• |

| 2.1     | Introduction (informative)                         |        |

| 2.2     | Literal value syntax                               |        |

| 2.3     | Integer and logic literals                         |        |

| 2.4     | Real literals                                      |        |

| 2.5     | Time literals                                      |        |

| 2.6     | String literals                                    |        |

| 2.7     | Array literals                                     |        |

| 2.8     | Structure literals                                 |        |

| Section | 3 Data Types                                       |        |

| 3.1     | Introduction (informative)                         |        |

| 3.2     | Data type syntax                                   |        |

| 3.3     | Integer data types                                 |        |

| 3.4     | Other basic data types                             |        |

| 3.5     | User-defined types                                 |        |

| 3.6     | Enumerations                                       |        |

| 3.7     | Structures and Unions                              |        |

| 3.8     | Casting                                            |        |

| Section | 4 Arrays                                           |        |

| 4.1     | Introduction (informative)                         |        |

| 4.2     | Packed and unpacked arrays                         |        |

| 4.3     | Multiple dimensions                                |        |

| 4.4     | Part selects (slices)                              |        |

| Section | 5 Data Declarations                                | •••••  |

| 5.1     | Introduction (informative)                         |        |

| 5.2     | Data declaration syntax                            |        |

| 5.3     | Constants                                          |        |

| 5.4     | Variables                                          |        |

| 5.5     | Scope and lifetime                                 |        |

| 5.6     | Nets, regs, and logic                              |        |

| Section | 6 Attributes                                       | •••••  |

| 6.1     | Introduction (informative)                         |        |

| 6.2     | Attribute syntax for interfaces                    |        |

| Section | 7 Operators and Expressions                        | •••••• |

| 7.1     | Introduction (informative)                         |        |

| 7.2     | Operator syntax                                    |        |

| 7.3     | Assignment, incrementor and decrementor operations |        |

| 7.4     | Operations on logic and bit types                  |        |

| 7.5     | Real operators                                     |        |

| 7.6     | Size                                               |        |

| 7.7     | Sign                                               |        |

| 7.8     | Operator precedence and associativity              |        |

| 10      |                                                    |        |

I

I

| Section 8 | Procedural Statements and Control Flow        | . 23  |

|-----------|-----------------------------------------------|-------|

| 8.1       | Introduction (informative)                    | . 23  |

| 8.2       | Blocking and nonblocking assignments          | . 24  |

| 8.3       | Selection statements                          | . 25  |

| 8.4       | Transition statements                         | . 26  |

| 8.5       | Loops statements                              | . 26  |

| 8.6       | Jump statements                               | . 26  |

| 8.7       | Named blocks and statement labels             | . 27  |

| 8.8       | Processes                                     | . 28  |

| 8.9       | Disable                                       | . 28  |

| 8.10      | Delay and Event control                       | . 29  |

| Section 9 | State Machines                                | . 31  |

| 9.1       | Introduction (informative)                    | . 31  |

| 9.2       | State machine constructs                      | . 31  |

| 9.3       | State declarations                            | . 33  |

| 9.4       | Transition statements                         | . 34  |

| 9.5       | Hierarchical and concurrent state machines    | . 36  |

| Section 1 | 0 Processes                                   | . 39  |

| 10.1      | Introduction (informative)                    | . 39  |

|           | Level sensitive logic                         |       |

|           | Latch sensitive logic                         |       |

|           | Edge sensitive logic                          |       |

|           | Continuous assignments                        |       |

|           | Static Process labels                         |       |

|           | Dynamic processes                             |       |

| Section 1 | 1 Tasks and Functions                         | . 43  |

|           | Introduction (informative)                    |       |

|           | Tasks                                         |       |

|           | Functions                                     |       |

| Section 1 | 2 Hierarchy                                   | 47    |

|           | Introduction (informative)                    |       |

|           | The \$root top level                          |       |

|           | Module declarations                           |       |

|           | Notice declarations                           |       |

|           | Port declarations                             |       |

|           | Time unit and precision                       |       |

|           | Module instances                              |       |

|           | Port connection rules                         |       |

|           | Name spaces                                   |       |

|           | Herarchical names                             |       |

|           | 3 Interfaces                                  |       |

|           | Introduction (informative)                    |       |

|           |                                               |       |

|           | Interface syntax                              |       |

|           | Ports in interfaces                           |       |

|           | Modports<br>Tasks and Functions in Interfaces |       |

|           | Parameterized interfaces                      |       |

|           | Access without Ports                          |       |

| 15./      |                                               | . / 1 |

| Section 14 Parameters                          |

|------------------------------------------------|

| 14.1 Introduction (informative)                |

| 14.2 Syntax                                    |

| Section 15 Configuration libraries             |

| 15.1 Introduction (informative)75              |

| 15.2 Libraries                                 |

| 15.3 Library map files                         |

| Section 16 System tasks and system functions77 |

| 16.1 Introduction (informative)                |

| 16.2 The \$bits system function                |

| Section 17 Compiler Directives                 |

| 17.1 Introduction (informative)                |

| 17.2 'define macros                            |

| Section 18 Assertions                          |

| Section 19 Recommended items for deprecation   |

| Annex A Formal Syntax                          |

| Annex B Keywords                               |

| Annex C Glossary                               |

| Annex D Bibliography                           |

# Section 1 Introduction to SystemVerilog

This document specifies the Accellera extensions for a higher level of abstraction for modeling and verification with the Verilog Hardware Description Language. Much of the syntax and semantics in these extensions are part of the SUPERLOG Extended Synthesis Subset (ESS) donation made to Accellera by Co-Design Automation, Inc. and proven with their products. SUPERLOG was developed by Peter Flake and Simon Davidmann to extend Verilog into the systems space and the verification space and was built on top of the work of the IEEE Verilog 2001 committee.

Throughout this document:

- "Verilog" or "Verilog-2001" refers to the IEEE Std. 1364-2001 standard for the Verilog Hardware Description Language

- "SystemVerilog" refers to the Accellera extensions to the Verilog-2001 standard.

This document numbers the generations of Verilog as follows:

- "Verilog 0.0" is the original Verilog language, first developed by Gateway Design Automation in 1984

- "Verilog 1.0" is the Open Verilog International (OVI) public version of Verilog released in 1990, which

was standardized by the IEEE in 1995 as IEEE Std. 1364-1995

- "Verilog 2.0" is the IEEE Std. 1364-2001 Verilog standard, commonly called Verilog-2001; this generation of Verilog contains the first significant enhancements to Verilog since its release to the public in 1990

- -- "SystemVerilog 3.0" is Verilog-2001 plus an extensive set of high-level abstraction extensions, as defined in this document

The Accellera initiative to extend Verilog is an on going effort under the direction of the Accellera HDL+ Technical Subcommittee. This committee will continue to define additional enhancements to Verilog beyond SystemVerilog 3.0.

SystemVerilog 3.0 is built on top of Verilog 2001. SystemVerilog improves the productivity, readability, and reusability of Verilog based code. The language enhancements in SystemVerilog provide more concise hardware descriptions while still providing an easy route with existing tools into current hardware implementation flows.

SystemVerilog adds several new constructs to Verilog-2001, including:

- C data types to provide better encapsulation and compactness of code

- int, char, typedef, struct, union, enum

- Enhancements to existing Verilog constructs, to provide tighter specifications

- Extensions to always blocks to include linting type features

- Logic (0, 1, X, Z) and bit (0, 1) data types

- Automatic/static specification on a per variable instance basis

- Procedural break, continue, return

- Interfaces to encapsulate communication and facilitate "Communication Oriented" design

- State Machines for designing control logic in compact and readable form

- Dynamic processes for modeling pipelines

- A \$root top level hierarchy which can have global definitions

# Section 2 Lexical Conventions Literal Values

# 2.1 Introduction (informative)

The lexical conventions for SystemVerilog literal values are extensions of those for Verilog. SystemVerilog adds literal time values, literal array values, literal structures and enhancements to literal strings.

# 2.2 Literal value syntax

[BNF excerpt to be inserted after BNF is approved]

Syntax 2-1—Literal values

# 2.3 Integer and logic literals

Literal integer and logic values can be sized or unsized, and follow the same rules for signedness, truncation and left-extending as Verilog-2001.

System Verilog adds the ability to specify unsized literal single bit values with a preceding apostrophe ( ' ), but without the base specifier. All bits of the unsized value are set to the value of the specified bit.

'0, '1, 'X, 'x, 'Z, 'z  $\,$  // sets all bits to this value

# 2.4 Real literals

The default type is **real** for fixed point format (e.g. 1.2), and exponent format (e.g. 2.0e10).

A cast can be used to convert literal real values to the **shortreal** type (e.g. shortreal'(1.2)). Casting is described in section 3.8.

## 2.5 Time literals

Time is written in integer or fixed point format, followed without a space by a time unit (fs ps ns us ms s). For example:

0.1ns 40ps

### 2.6 String literals

A string literal is enclosed in quotes and has its own data type. Non-printing and other special characters are preceded with a backslash. SystemVerilog adds the following special string characters:

\v vertical tab \f form feed \a bell \x02 hex number

A string literal can be cast to a character, or a packed array, as in Verilog-2001. If the size differs, it is right justified.

char c1 = "A" ; bit [7:0] d = "\n" ; bit [0:11] [7:0] c2 = "hello world\n" ;

A string literal can be cast to an unpacked array of characters, and a zero termination is added like in C. If the size differs, it is left justified.

```

char c3 [0:12] = "hello world\n" ;

```

Packed and unpacked arrays are discussed in section 4.

#### 2.7 Array literals

Arrays literals are similar to C initializers, but with the repeat operator ( { { } } ) allowed

int n[1:2][1:3] = {{0,1,2},{3{4}}};

The nesting of braces must follow the number of dimensions, unlike in C. However, repeat operators can be nested:

int n[1:2][1:3] = {2{{3{4}}}};

If the type is not given by the context, it must be specified with a cast

typedef int [1:3] triple; // 3 integers packed together b = triple'{0,1,2};

#### 2.8 Structure literals

Structure literals are similar to C initializers. Structure literals must have a type, either from context or a cast:

```

typedef struct {int a; shortreal b;} ab;

ab c;

c = {0, 0.0}; // structure literal type determined from the left hand context

(c)

```

Nested braces should reflect the structure, for example:

ab abarr[1:0] =  $\{\{1, 1.0\}, \{2, 2.0\}\};$

Note that the C alternative  $\{1, 1.0, 2, 2.0\}$  is not allowed.

# Section 3 Data Types

# 3.1 Introduction (informative)

To provide for clear translation to and from C, SystemVerilog supports the C built-in types, with the meaning given by the implementation C compiler. However, to avoid the duplication of **int** and **long** without causing confusion, in SystemVerilog, **int** is 32 bits and **longint** is 64 bits. The C **float** type is called **shortreal** in SystemVerilog, so that it will not be confused with the Verilog-2001 **real** type.

Verilog-2001 has net data types, which may have 0, 1, X or Z, plus 7 strengths, giving 120 values. It also has variable data types such as **reg**, which have 4 values 0, 1, X, Z. These are not just different data types, they are used differently. SystemVerilog adds another 4-value data type, called **logic**. See section 3.3.1.

Verilog-2001 provides arbitrary fixed length arithmetic using **reg** data types. The **reg** type can have bits at X or Z, however, and so are less efficient than an array of bits because the operator evaluation must check for X and Z, and twice as much data must be stored. SystemVerilog adds a **bit** type which can only have bits with 0 or 1 values. See section 3.3.1.

Automatic type conversions from a smaller number of bits to a larger number of bits involve zero extensions if unsigned or sign extensions if signed, and do not cause warning messages. Automatic truncation from a larger number of bits to a smaller number does cause a warning message. Automatic conversions between logic and bit do not cause warning messages. To convert a logic value to a bit, 1 converts to 1, anything else to 0.

User defined types are introduced by typedef and must be defined before they are used. Data types can also be parameters to modules or interfaces, making them like class templates in object-oriented programming. One routine can be written to reverse the order of elements in any array, which is impossible in C and in Verilog.

Structures and unions are complicated in C because the tags have a separate name space. SystemVerilog follows the C syntax, but without the optional structure tags.

See also Section 4 on arrays.

# 3.2 Data type syntax

| [BNF | excerpt | to | be | inserted | after | BNF | is | approved] |

|------|---------|----|----|----------|-------|-----|----|-----------|

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

|      |         |    |    |          |       |     |    |           |

Syntax 3-2—data types

# 3.3 Integer data types

SystemVerilog offers several integer data types, representing a hybrid of both Verilog and C data types:

| char     | 2-state C data type, usually an 8 bit signed integer (ASCII) or a short int (Unicode)       |  |  |  |

|----------|---------------------------------------------------------------------------------------------|--|--|--|

| shortint | 2-state SystemVerilog data type, 16 bit signed integer                                      |  |  |  |

| int      | 2-state SystemVerilog data type, 32 bit signed integer                                      |  |  |  |

| longint  | 2-state SystemVerilog data type, 64 bit signed integer                                      |  |  |  |

| byte     | 2-state SystemVerilog data type, 8 bit signed integer                                       |  |  |  |

| bit      | 2-state SystemVerilog data type, user-defined vector size                                   |  |  |  |

| logic    | 4-state SystemVerilog data type, user-defined vector size with different use rules from reg |  |  |  |

| reg      | 4-state Verilog-2001 data type, user-defined vector size                                    |  |  |  |

| integer  | 4-state Verilog-2001 data type, at least 32 bit signed integer                              |  |  |  |

### Table 3-1—Integer data types

#### 3.3.1 2-state (two-value) and 4-state (four-value) data types

Types which can have unknown and high impedance values are called 4-state types. These are logic, reg and integer. The other types do not have unknown values and are called 2-state types, for example bit and int.

The difference between **int** and **integer** is that **int** is 2-state logic and **integer** is 4-state logic. 4-state values have additional bits that encode the X and Z states. 2-state data types should simulate faster, take less memory, and are preferred in some design styles.

#### 3.3.2 Signed and unsigned data types

Integer types use integer arithmetic and can be signed or unsigned. This affects the meaning of certain operators such as '<', etc.

int unsigned ui;

int signed si;

The data types char, byte, shortint, int, integer and longint default to signed. The data types bit, reg and logic default to unsigned, as do arrays of these types.

Note that the **signed** keyword is part of Verilog-2001. The **unsigned** keyword is a reserved keyword in Verilog-2001, but is not utilized.

See also section 7, on operators and expressions.

#### 3.4 Other basic data types

#### 3.4.1 Time data types

Time is a special data type. It is a 64 bit integer of time steps. The default time step follows the rules of IEEE Verilog standard. The time step can be changed by the **timeprecision** declaration. It can also be changed by a **`timescale** directive.

The timeprecision declaration affects the local accuracy of delays

```

module m;

timeprecision 0.1ns;

initial #10.11ns a = 1; // round to #10.1ns according to time precision

endmodule

```

The timeunit declaration is used to set the current time unit. When a literal time is expressed in SystemVerilog, it can be given with explicit time units, e.g. 12ns. If no time units are specified, the literal number is multiplied by the current time unit. Time values are scaled to the time precision of the module, following the rules of Verilog-2001. An integer or real variable is cast to a time value by using the integer or real as a delay.

For example

#10.11; // multiply by time unit and round according to time precision

See section 12.6 on for more information on setting the time units and time precision.

#### 3.4.2 Real and shortreal data types

The **real**<sup>1</sup> data type is from Verilog-2001, and is the same as a C **double**. The **shortreal** data type is a SystemVerilog data type, and is the same as a C **float**.

<sup>&</sup>lt;sup>1</sup> The real and shortreal types are represented as described by IEEE 734-1985, an IEEE standard for floating point numbers.

#### 3.4.3 Void data type

The **void** data type represents non-existent data. This type can be specified as the return type of functions, indicating no return value.

### 3.5 User-defined types

```

[BNF excerpt to be inserted after BNF is approved]

```

The user can define a new type using typedef, as in C.

typedef int intP;

This can then be instantiated:

intP a, b;

A type can be used before it is defined, provided it is first identified as a type by an empty typedef:

typedef foo; foo f = 1; typedef int foo;

Note that this does not apply to enumeration values, which must be defined before they are used.

If the type is defined within an interface it must be re-defined locally before being used.

```

interface it;

typedef int intP;

endinterface

it it1;

typedef it1.intP intP;

```

User-defined type names must be used for complex data types in casting (see section 3.7, below), and as parameters.

#### 3.6 Enumerations

An enumerated type has one of a set of named values.

enum {red, yellow, green} light1, light2; // `anonymous' type

The values can be cast to integer types, and increment from an initial value of 0. This can be over-ridden.

enum {bronze=3, silver, gold} medal; // silver=4, gold=5

A sized constant can be used to set the size of the type. All sizes must be the same.

enum {bronze=4'h3, silver, gold} medal4; // 4 bits wide

A type name can be given so that the same type can be used in many places.

typedef enum {NO, YES} boolean; boolean myvar; // named type

The type is checked in assignments, arguments and relational operators (which check the values). Like C, there is no overloading of literals, so medal and medal4 cannot be defined in the same scope, since they contain the same names.

# 3.7 Structures and Unions

Structure and union declarations follow the C syntax, but without the optional structure tags before the '{'.

```

struct { bit[7:0] opcode; bit [23:0] addr; }IR; // anonymous structure defines

variable IR

IR.opcode = 1; // set field in IR.

```

Named structure types must always use typedef, as there is no equivalent of the C struct adjective, such as 'struct instruction IR;'. Some additional examples of declaring structure and unions are:

```

typedef struct {

bit[7:0] opcode;

bit [23:0] addr;

} instruction; // named structure type

instruction IR; // define variable

typedef union { int i; shortreal f; } num; // named union type

num n;

n.f = 0.0; // set n in floating point format

typedef struct {

bit isfloat;

union { int i; shortreal f; } n; // anonymous union type

} tagged; // named structure

tagged a[9:0]; // array of them

```

A structure can be assigned as a whole, and passed to or from a function or task as a whole. Note that it is inefficient to copy large structures. A structure can contain arrays, but a union cannot contain an array of variable size.

Section 2.8 discusses assigning initial values to a structure.

#### 3.8 Casting

I

A data type may be changed by using a cast ( ' ) operation.

int'(2.0 \* 3.0)

A decimal number as a data type means a number of bits.

17′(x - 2)

The signedness can also be changed.

per Peter's

e-mail

11 Mar 2002

per Peter's

e-mail

11 Mar 2002

signed' (x)

A user-defined type can be used.

mytype'(foo)

A complex data type cannot be used. It must be defined with a typedef.

When a **shortreal** is converted to an **int**, its value is rounded as in Verilog. So the conversion can lose information. When a **shortreal** is converted to 32 bits, its bit pattern is preserved, which means it can be converted back to the same value without any loss of information. This technique can also be used for structures, where the **\$bits** attribute gives the size of a structure in bits (the **\$bits** system function is discussed in section 16.2):

```

typedef struct {

bit isfloat;

union { int i; shortreal f; } n; // anonymous type

} tagged; // named structure

typedef bit [$bits(tagged) - 1 : 0] tagbits; // tagged defined above

tagbits t = tagbits'(a[3]); // convert structure to array of bits

a[4] = tagged't; // convert array of bits back to structure

```

Editor's note: Are parenthesis required around the casted value? The preceding line does not have them, but all other examples do..

Note that the **bit** data type loses X values. If these are to be preserved, the logic type should be used instead.

The size of a union in bits is the size of its largest member. The size of a logic in bits is 1.

For compatibility, the Verilog functions \$itor, \$rtoi, \$bitstoreal, \$realtobits, \$signed, \$unsigned can also be used.

# Section 4 Arrays

# 4.1 Introduction (informative)

In C, arrays are indexed from 0 by integers, or converted to pointers. Although the whole array can be initialized, each element must be read or written separately in procedural statements.

In Verilog-2001, arrays are indexed from left-bound to right-bound. If they are logie vectors, they can be assigned as a single unit, but not if they are arrays. Verilog-2001 allows multiple dimensions.

In Verilog-2001, all data types can be declared as arrays. The **reg**, **wire** and all other net types can also have a vector width declared. A dimension declared before the object name is referred to as the "vector width" dimension. The dimensions declared after the object name are referred to as the "array" dimensions.

reg [7:0] r1 [1:256]; // [7:0] is the vector width, [1:256] is the array size

SystemVerilog enhances array declarations in several ways.

# 4.2 Packed and unpacked arrays

SystemVerilog uses the term "*packed array*" to refer to the dimensions declared before the object name (what Verilog-2001 refers to as the vector width). The term "*unpacked array*" is used to refer to the dimensions declared after the object name.

Dense arrays of small data types such as bits can be stored packed (8 bits to a byte) or unpacked (1 bit to a word). This choice affects the efficiency of operations such as addition of bit vectors or selection of individual bits, and is similar to the Verilog-2001 notions of **vectored** and **scalared**. Assignments and arithmetic operations are allowed for packed arrays but not for unpacked. The **vectored** and **scalared** modifiers shall behave as defined in the IEEE Verilog standard. They may be used by software implementations to optimize performance.

Packed arrays can only be made of the single bit types: **bit**, **logic**, **reg**, **wire**, and the other net types. The dimensions are written to the left of the variable for a packed array, and to the right for an unpacked array.

bit [7:0] c1; // packed array

bit u [7:0]; // unpacked array

Packed arrays allow arbitrary length integer types, so a 48 bit integer can be made up of 48 bits. These integers can then be used for 48 bit arithmetic. The maximum size of a packed array may be limited, but shall be at least  $65536 (2^{16})$  bits.

Integer types with predefined widths cannot have packed array dimensions declared. These types are: **char**, **byte**, **shortint**, **int**, **longint**, and **integer**. An integer type with a predefined width can be treated as a single dimension packed array. The packed dimensions of these integer types shall be numbered down to 0, such that the right-most index is 0.

byte c2; // same as bit [7:0] c2; integer i1; // same as logic signed [31:0] i1;

# 4.3 Multiple dimensions

Like Verilog memories, the dimensions following the type set the packed size. The dimensions following the instance set the unpacked size, where access must be by index.

bit [3:0] [7:0] joe [1:10]; // 10 entries of 4 bytes (packed into 32 bit int)

can be used as follows:

joe[9] = joe[8] + 1; // 4 byte add

joe[7][3:2] = joe[6][1:0]; // 2 byte copy

Note that the dimensions declared following the type and before the name ([3:0] in the preceding example) vary more rapidly than the dimensions following the name ([1:10] in the preceding example). When used, the first dimensions ([3:0]) follow the second dimensions ([1:10]).

In a list of dimensions, the right-most one varies most rapidly, as in C. However a packed dimension varies more rapidly than an unpacked one.

Multiple packed dimensions can also be defined in stages with typedef:

```

typedef bit [1:5] bsix;

bsix [1:10] foo5; // 1 to 5 varies most rapidly

```

When the array is used with a smaller number of dimensions, these have to be the slowest varying ones:

bit [9:0] foo6; foo5 = foo1[2]; // a 10 bit quantity.

As in Verilog-2001, a comma-separated list of array declarations can be made. All arrays in the list will have the same data type and the same packed array dimensions.

**bit** [7:0] [31:0] foo7 [1:5] [1:10], foo8 [0:255]; // two arrays declared

If an index expression is of type logic vector a 4-state type, and the array is of type logic vector a 4-state type, an  $\mathbf{X}$  or  $\mathbf{Z}$  in the index expression will cause a read to return  $\mathbf{X}$ , and a write to issue a run-time warning. If an index expression is of type logic vector a 4-state type, but the array is not of type logic a 2-state type, an  $\mathbf{X}$  or  $\mathbf{Z}$  in the index expression will shall generate a run-time warning and be treated as  $\mathbf{0}$ . If an index expression is out of bounds, a run-time warning may be generated. This check can be turned off for efficiency.

Out of range index values shall be illegal for both reading from and writing to an array of 2-state variables, such as int. The result of an out of range index value is indeterminate. Implementations shall generate a warning if an out of range index occurs for a read or write operation.

#### 4.4 Part selects (slices)

An expression can select part of a packed array, or indeed any integer type, which is assumed to be numbered down to 0:

```

int j = 0;

shortint msh = j[31:16];

```

The size of the part must be constant, but the position may be variable. The syntax of Verilog-2001 is used:

int i = bitvec[j +: k]; // k must be constant.

a = {(b[c -: d]), e}; // d must be constant

Slices (part selects) of an array can only apply to one dimension, but other dimensions may have single index values in an expression.

# Section 5 Data Declarations

# **5.1 Introduction** (informative)

There are several forms of data in SystemVerilog: macros (see section 17), literals (see section 2), parameters (see section 14), constants, variables, nets, and attributes (see section 6)

C constants are either literals, macros or enumerations. There is also a **const**, keyword but it is not enforced in C.

Verilog 2001 constants are literals, parameters, localparams, specparams or macros. Verilog 2001 also has variables and nets. Variables must be written by procedural statements and nets must be written by continuous assignments or ports.

SystemVerilog follows Verilog by requiring data to be declared before it is used, apart from implicit nets. The rules for implicit nets are the same as in Verilog-2001.

A variable can be static (storage allocated on instantiation and never de-allocated) or automatic (stack storage allocated on entry to a task, function or named block and de-allocated on exit). C has the keywords **static** and **auto**. SystemVerilog follows Verilog in respect of the static default storage class, with automatic tasks and functions, but allows **static** to override a default of **automatic** for a particular variable in such tasks and functions.

# 5.2 Data declaration syntax

[BNF excerpt to be inserted after BNF is approved]

per Peter's

e-mail

11 Mar 2002

# 5.3 Constants

Constants are named data items which never change. SystemVerilog allows any data type to be declared as constant, with the **const** keyword.

const char colon = ":" ;

A constant expression contains literals and other named constants.

SystemVerilog enhancements to **parameter** constant declarations are presented in section 14. SystemVerilog does not change **localparam** and **specparam** constants declarations. A **const** form of constant differs from a **localparam** constant in that the **localparam** must be set during elaboration, whereas a **const** can be set during simulation, such as in an automatic task.-

Editor's note: Suggest integrating contents of section 14 here, and deleting section 14.

#### 5.4 Variables

A variable declaration consists of a data type followed by one or more instances.

```

shortint s1, s2[0:9];

```

A variable can be declared with an initializer, which must be a constant expression:

**int** i = 0;

In Verilog-2001, an initialization value specified as part of the declaration is executed as if the assignment were made from an initial block, after simulation has started. Therefore, the initialization may cause an event on that variable at simulation time zero.

In SystemVerilog, setting the initial value of a static variable as part of the variable declaration shall occur before any **initial** or **always** blocks are started and so does not generate an event. If an event is needed, an **initial** block should be used to assign the initial values.

#### 5.5 Scope and lifetime

Any data declared outside a module, interface, task, or function, is global in scope (can be used anywhere after its declaration) and has a static lifetime (exists for the whole elaboration and simulation time).

SystemVerilog data declared inside a module or interface but outside a task, process or function is local in scope and static in lifetime (exists for the lifetime of the module or interface). This is roughly equivalent to C static data declared outside a function, which is local to a file.

Data declared in an automatic task, function or block has the lifetime of the call or activation and a local scope. This is roughly equivalent to a C automatic variable. Data declared in a dynamic process is also automatic.

Data declared in a static task, function or block defaults to a static lifetime and a local scope. If an initializer is used, the keyword **static** must be specified to make the code clearer.

Note that in SystemVerilog, data can be declared in unnamed blocks as well as in named blocks, but in the unnamed blocks a hierarchical name cannot be used to access it.

Verilog-2001 allows tasks and functions to be declared as **automatic**, making all storage within the task or function automatic. SystemVerilog allows specific data within a static task or function to be explicitly declared as **automatic**. Data declared as automatic has the lifetime of the call or block, and is initialized on each entry to the call or block.

per mtg. 19 18 Mar 2002

SystemVerilog also allows data to be explicitly declared as **static**. Data declared to be **static** in an automatic task, function or in a process has a static lifetime but and a scope local to the block. This is like C static data declared within a function.

```

module msl;

int st0; // static

initial begin

int st1; //static

static int st2; //static

automatic int autol; //automatic

end

task automatic t1();

int auto2; //automatic

static int st3; //static

automatic int auto3; //automatic

endtask

endmodule

```

Note that automatic variables cannot be used to trigger an event expression or be written with a nonblocking assignment.

See also section 11 on tasks and functions.

5.6 Net declarations

[BNF excerpt to be inserted after BNF is approved]

#### 5.6 Nets, regs, and logic

A net can only be written by one or more continuous assignments, primitive outputs or through module ports. The resultant value of multiple drivers is determined by the resolution function of the net type. The value can be overridden by a **force** statement. If a net on one side of a port is driven by a variable on the other side, a continuous assignment is implied.

A register reg variable can only be written by one or more procedural statements, including procedural (quasi-) continuous assignments. The last write determines the value. The force statement overrides the assign statement which overrides the normal assignments. A register reg variable cannot be written through a port.

A logic variable can be written either by one continuous assignment or primitive output, or by one or more procedural statements. The last write determines the value. A logic variable can be written through a port. It shall be an error to have a continuous assignment and a procedural assignment write to the same logic variable, even through ports. The **assign** statement overrides normal procedural assignments to a logic variable, until deassigned.

Note the difference between a net declaration with assignment and a variable initialization:

wire w = vara & varb; // continuous assignment

reg r = consta & constb; // initial assignment

logic v = consta & constb; // initial assignment

# Section 6 Attributes

# 6.1 Introduction (informative)

With Verilog-2001, users can add named attributes (properties) to Verilog objects, such as modules, instances, wires, etc. The SystemVerilog extends the attribute syntax to support interfaces. The SystemVerilog also defines a default data type for attributes.

# 6.2 Attribute syntax for interfaces

[BNF excerpt to be inserted after BNF is approved]

### Syntax 6-5—Interface attribute syntax

An example of defining an attribute for an interface declaration is:

(\* interface\_att = 10 \*) interface bus1.... endinterface

The default type of an attribute with no value is **bit**, with a value of 1. Otherwise, the attribute takes the type of the expression.

The modport declaration can be preceded by an attribute instance, like any other interface item.-

per Peter's e-mail after mtg. 19 19 Mar 2002

# Section 7 Operators and Expressions

# 7.1 Introduction (informative)

The SystemVerilog operators are a combination of Verilog and C operators. In both languages, the type and size of the operands is fixed, and hence the operator is of a fixed type and size. The fixed type and size of operators is preserved in SystemVerilog. This allows efficient code generation.

per Stu's e-mail 25 Mar 2002

Verilog does not have assignment operators or incrementor and decrementor operators. SystemVerilog includes the C assignment operators, such as +=, and the C incrementor and decrementor operators, ++ and --.

Verilog-2001 added signed nets and registers reg variables, and signed based literals. There is a difference in the rules for combining signed and unsigned integers between Verilog and C. SystemVerilog uses the Verilog-2001 rules.

Editor's note: Suggest the preceding paragraph be moved to normative section 7.7.

The fixed type and size of operators is preserved in SystemVerilog.

In Verilog-2001, the size is the maximum of the operands and the context, with unsigned winning whether it is bigger or not. This is likely to give unexpected behavior — adding a carry bit can make a signed result unsigned. An example of this in Verilog is:

per Stu's e-mail 25 Mar 2002

parameter p1 = -10 + h1; // this is unsignedwire [63:0] w1 = p1;wire [31:0] w2 = p1;

# 7.2 Operator syntax

[BNF excerpt to be inserted after BNF is approved]

Syntax 7-6—Operator syntax

# 7.3 Assignment, incrementor and decrementor operations

In addition to the simple assignment operator, =, SystemVerilog includes the C assignment operators and special bitwise assignment operators: +=, -=, \*=, /=, &=, |=, ^=, <<=, and >>>=. Assignment operators may only be used with blocking assignments.

per Stu's e-mail 25 Mar 2002

In SystemVerilog, an expression can include a blocking assignment, provided it does not have a timing control. Note that such an assignment must be enclosed in parentheses to avoid common mistakes such as using a=b for a=b, or  $a \mid =b$  for  $a \mid =b$ . Assignment operators may only be used with blocking assignments.

if ((a=b)) b = (a+=1);

a = (b = (c = 5));

SystemVerilog also includes the C incrementor and decrementor operators ++i, --i, i++, and i-- (provided there is no timing control). These can be used in expressions without parentheses. These increment and decrement operations behave as blocking assignments.

# 7.4 Operations on logic and bit types

When a binary operator has one operand of type **bit** and another of type **logic**, the result is of type **logic**. If one operand is of type **int** and the other of type **integer**, the result is of type **integer**.

The operators != and == return an X if either operand contains an **x** or a **z**, as in Verilog-2001. This is converted to a 0 if the result is converted to type **bit**, e.g. in an **if** statement. The operators !== and === match 25 Mar 2002 Xs and Zs exactly.

The expression bit'(1'bX ? 1'b0 : 1'b1) returns 0 not 1 because the X on the selector produces an X on the ternary operator output, which is converted to 0 by the cast to bit.

The operators || and && provide 'short-circuit' evaluation as follows:

| <del>a()    b ();</del>        | <pre>// b is not evaluated if a returns 1.</pre> |

|--------------------------------|--------------------------------------------------|

| <del>a() &amp;&amp; b();</del> | <pre>// b is not evaluated if a returns 0;</pre> |

Note that b is evaluated if a returns X.

To avoid short-circuit evaluation use a bitwise operator

```

a() = 0 | b() = 0; // b is always evaluated

```

The unary reduction operators ( $\mathbf{a} \sim \mathbf{a} \mid \mathbf{a} \mid \mathbf{a} \sim \mathbf{a}$ ) can be applied to any packed type, including multi-dimensional packed arrays. The operators shall return a single value of type **logic** if the packed type is four valued, and of type **bit** if the packed type is two valued.

```

int i;

bit b = &i;

integer j;

logic c = &j;

```

#### 7.5 Real operators

Real and shortreal operands are allowed with the following unary operators (the increment is by 1.0):

+-++--!

Real and shortreal operands are allowed with the following binary and ternary operators:

```

+<u>*</u>/

>>=<<=

&& ||

== !=

?;

```

Operands of type **shortreal** have the same operation restrictions as Verilog **real** operands. The unary operators ++ and -- may have operands of type **real** and **shortreal** (the increment is by 1.0).

Editor's note: Preceding change made to emphasize what is different in SystemVerilog. QUESTION: What assignment operators are legal/illegal with real operands?

If any operand is **real**, the result is **real**, except before the ? in the ternary operator. If no operand is **real** and any operand is **shortreal**, the result is **shortreal**.

Real operands can also be used in the following expressions:

str.realval // structure or union member realarray[intval] // array element

# 7.6 Size

The number of bits of an expression is determined by the operands and the context, following the same rules as in Verilog-2001. In SystemVerilog, casting can be used to set the size context of an intermediate value.

A tool may warn With Verilog, some tools may issue a warning when the left and right hand sides of an assignment are different sizes. Using the SystemVerilog size casting, these warnings can be prevented by using casts.

# 7.7 Sign

The following unary operators give the signedness of the operand:  $\sim ++ -- + -$ . All other operators shall follow the same rules as Verilog for performing signed and unsigned operations.

# 7.8 Operator precedence and associativity

Operator precedence and associativity is listed in table 7-2, below. The highest precedence is listed first.

| () [] -> .                                  | left          |

|---------------------------------------------|---------------|

| Unary ! ~ ++ + - & ~& &&   ~     ^ ~^       | right         |

| **                                          | left          |

| * / %                                       | left          |

| + -                                         | left          |

| << >> <<< >>>                               | left          |

| < <= > >=                                   | left          |

| == != === !==                               | left          |

| &                                           | left          |

| ^ ~^                                        | left          |

|                                             | left          |

| &&                                          | left          |

|                                             | left          |

| ?:                                          | right         |

| = += -= *= /= %= &= ^=  = <<= >>= <<<= >>>= | none          |

| {,}                                         | concatenation |

Note that  $\mathbf{a}$  is higher precedence than  $^{\text{,}}$  following the Verilog standard.

## 7.9 Concatenation

Braces ( { } ) are used to show concatenation, as in Verilog. The concatenation is treated as a packed vector of **bits** (or **logic** if any operand is of type **logic**). It can be used on the left hand side of an assignment or in an expression:

```

logic log1, log2, log3;

{log1, log2, log3} = 3'b111;

{log1, log2, log3} = {1'b1, 1'b1, 1'b1}; // same effect as 3'b111

```

Software tools may generate a warning if the concatenation width on one side of an assignment is different than the expression on the other side. The following examples may give warning of size mismatch:

```

bit [1:0] packedbits = {1,1}; // right hand side is 64 bits

int i = {1'b1, 1'b1}; //right hand side is 2 bits

```

Editor's note: The concatenation {1,1} is illegal in Verilog, which only permits sized literals in concatenation. If unsized literals are allowed in SystemVerilog, this new feature needs to be described.

Note that braces are also used for initializers of structures or unpacked arrays. Unlike in C, the expressions must match element for element and the braces must match the structures and array dimensions. Each element must match the type being initialized, so the following do not give size warnings:

```

bit unpackedbits [1:0] = {1,1}; // no size warning, bit can be set to 1

int unpackedints [1:0] = {1'b1,1'b1}; //no size warning, int can be set to 1'b1

```

Multiple concatenation can be used for initializers as well e.g.  $\{3\{1\}\}$  for  $\{1, 1, 1\}$ .

Refer to sections 2.7 and 2.8 for more information on initializing arrays and structures .

# Section 8 Procedural Statements and Control Flow

# 8.1 Introduction (informative)

Procedural statements are introduced by one of:

initial // do this statement once

always, always\_comb, always\_latch, always\_ff // loop forever (see section 10 on processes)

task // do these statements whenever the task is called

function // do these statements whenever the function is called and return a value

SystemVerilog has the following types of control flow within a process

- Selection, loops and jumps

- Task and function calls

- Sequential and parallel blocks

- Timing control

Verilog procedural statements are in initial or always blocks, tasks or functions.

Verilog includes most of the statement types of C, except for do...while, break, continue and goto. Verilog has the **repeat** statement which C does not, and the **disable**. The use of the Verilog **disable** to carry out the functionality of break and continue requires the user to invent block names, and introduces the opportunity for error.

SystemVerilog adds C-like break, continue and return functionality, which do not require the use of block names.

Loops with a test at the end are sometimes useful to save duplication of the loop body. SystemVerilog adds a C-like do...while loop for this capability.

[BNF excerpt to be inserted after BNF is approved]

Syntax 8-7—Statement syntax

23

# 8.2 Blocking and nonblocking assignments

```

[BNF excerpt to be inserted after BNF is approved]

```

The following assignments are allowed in both Verilog-2001 and SystemVerilog:

#1 r = a; r = #1 a; r <= #1 a; r <= a; @c r = a; r = @c a; r <= @c a;</pre>

SystemVerilog also allows a time unit to specified in the assignment statement, as follows:

#lns r = a; r = #lns a; r <= #lns a;</pre>

It shall be illegal to make nonblocking assignments to automatic variables are not allowed.

The size of the left-hand side of an assignment forms the context for the right hand side expression. If the lefthand side is smaller than the right hand side, and information may be lost, a warning is can be given. Nonblocking assignments to automatic variables are not allowed.

per Stu's e-mail 28 Mar 2002

## 8.3 Selection statements

[BNF excerpt to be inserted after BNF is approved]

Syntax 8-9—Selection statement syntax

```

if (condition) statement // as Verilog or C

if (condition) statement else statement

```

per Stu's e-mail 28 Mar 2002

The condition is evaluated as a boolean, so that 0 or X or In Verilog, an **if** (expression) is evaluated as a boolean, so that if the result of the expression is 0 or X, the test is considered false. With SystemVerilog, **null** or **void** or {} are also false, and any other values are true.

System Verilog adds the keywords unique and priority, which can be used before an if. In the case of an else...if, the unique indicates that the conditions do not overlap. If either keyword is used it is shall be a runtime warning for no condition to match unless there is an explicit else. For example:

```

unique if((a==0) || (a==1)) $display(" 0 or 1");

else if (a == 2) $display("2");

else if (a == 4) $display("4"); // values 3,5,6,7 will cause a warning

priority if(a[2:1]==0) $display(" 0 or 1");

else if (a[2] == 0) $display("2 or 3");

else $display(" 4 to 7"); //covers all other possible values, so no warning

```

In the case of the unique if, there is no overlap in the conditions, allowing the expressions to be evaluated in parallel. With the priority if, if the variable 'a' in the preceding example had a value of 0, it would satisfy both the first and second conditions, requiring priority logic.

A unique if indicates that there should not be any overlap in a series of if...else...if conditions, allowing the expressions to be evaluated in parallel. A software tool shall issue an error if it determines that there is a potential overlap in the conditions.

A **priority** if indicates that a series of if...else...if conditions shall be evaluated in the order listed. In the preceding example, if the variable 'a' had a value of 0, it would satisfy both the first and second conditions, requiring priority logic.

In Verilog 2001, there are three types of case statements, introduced by case, casez and casex. With SystemVerilog, each of these can be qualified by priority or unique. A priority case shall acts on the first match only. A unique case shall guarantees no overlapping case values, allowing the case items to be evaluated in parallel. If the case is qualified as priority or unique, the simulator shall issues a warning message if an unexpected case value is found. The user does not need By specifying unique or priority, it is not necessary to code a default case to trap unexpected case values.

For example

```

bit[2:0] a;

unique case(a) // values 3,5,6,7 will cause a run-time warning

0,1: $display(" 0 or 1 ");

2: $display("2");

4: $display("4");

endcase

priority casez(a)

2'b00?: $display(" 0 or 1 ");

2'b0??: $display(" 2 or 3 ");

default: $display(" 4 to 7");

endcase

```

The unique and priority keywords shall determine the simulation behavior. It is recommended that synthesis follow simulation behavior where possible. Attributes may also be used to determine synthesis behavior.

# 8.4 Transition statements

The transition statement is used in state machine modeling, and discussed in section 9 on state machines.

### 8.5 Loops statements

[BNF excerpt to be inserted after BNF is approved]

#### Syntax 8-10—Loop statement syntax

Verilog-2001 provides for, while, repeat and forever loops. SystemVerilog adds a do...while loop:

do statement while(condition) // as C

The condition can be any expression which can be treated as a boolean. It is evaluated after the statement.

#### 8.6 Jump statements

[BNF excerpt to be inserted after BNF is approved]

#### Syntax 8-11—Jump statement syntax

SystemVerilog adds the C jump statements break, continue and return.

break // out of loop as C

continue // skip to end of loop as C

return expression // exit from a function

return // exit from a task or void function

Note that SystemVerilog does not include the C goto statement.

#### 8.7 Named blocks and statement labels

Verilog-2001 allows a begin...end or fork...join statement block to be named. A named block is used to identify the entire statement block. A named block creates a new hierarchy scope. The block name is specified after the begin or fork keyword, preceded by a colon. For example:

```

begin : blockA // Verilog-2001 named block

...

end

```

SystemVerilog allows a matching block name to be specified after the block **end** or **join** keyword, preceded by a colon. This can help document which **end** or **join** is associated with which **begin** or **fork** when there are nested blocks. A name at the end of the block is not required. It is shall be an error if the name at the end is different than the block name at the beginning.

```

per Stu's e-mail

28 Mar 2002

```

```

begin: blockB // block name after the begin or fork

...

end: blockB

```

SystemVerilog allows a label to be specified before any statement, as in C. A statement label is used to identify a single statement. A statement label does not create a hierarchy scope. The label name is specified before the statement, followed by a colon.

labelA: statement

A begin...end or fork...join block is considered a statement, and can have a statement label before the block. This is not the same as a block name, however, because it does not create a hierarchy scope.

```

labelB: fork // label before the begin or fork

...

join : labelB

```

A label at the end of the block is not required. It is shall be an error if the label at the end is different than the label at the beginning.

It shall be illegal to have both a label before a **begin** or **fork** and a block name after the **begin** or **fork**. A label cannot appear before the **end** or **join**, as these keywords do not form a statement.

#### 8.8 Processes

Each **initial** and **always** block is a process. Each branch of a **fork** within such a block is also a process. These are static processes and they can be explicitly named with a statement label as shown above.

A new (dynamic) process can be created by the **process** keyword. This forks off a statement without waiting for completion:

process statement

See Section 10 for more information about processes.

#### 8.9 Disable

SystemVerilog has **break** and **continue** for a clean way to break out of or continue the execution of loops. The Verilog-2001 disable can also be used to break out of or continue a loop, but is more awkward than using **break** or **continue**. The **disable** is also allowed to disable a named block, which does not contain the **disable** statement. If the block is currently executing, this causes control to jump to the statement immediately after the block. If the block is a loop body, it acts like a **continue**. If the block is not currently executing, the **disable** has no effect. The **disable**, **break** and **continue** statements shall not affect any nonblocking assignments which have been started.

It shall be illegal to disable a function because the return value would be uncertain. However a function may disable its calling block.

System Verilog has **return** from a task, but **disable** is also supported. If **disable** is applied to a named task, all current executions of the task are disabled.

```

module ...

always always1: begin ... t1: task1( ); ... end

...

endmodule

always begin

...

disable u1.always1.t1; // exit task1, which was called from always1

(static)

end

```

8.10 Delay and Event control

[BNF excerpt to be inserted after BNF is approved]

Syntax 8-13—Delay and event control syntax

SystemVerilog has #time or #(time\_expression) as a delay control, like Verilog-2001.

Any change in a variable or net can be detected using the @ event control, as in Verilog. If the expression evaluates to a result of more than one bit, a change on any of the bits of the result (including an x to z change) will trigger the event control.

SystemVerilog adds the following enhancement: an iff qualifier to the @ event control.

```

module latch (output logic [31:0] y, input [31:0] a, input enable);

always @(a iff enable == 1)

y <= a; //latch is in transparent mode

endmodule</pre>

```

The event expression only triggers if the expression after the iff is true, in this case when rst ==0. Note that such an expression is evaluated when clk changes not when rst changes. Also note that iff has precedence over or. This can be made clearer by the use of parentheses.

If a variable or net is not of type logic, then posedge and negedge refer to transitions from 0 and to 0 respectively. If the variable or net is a dense packed array or structure, it is zero if all elements are 0.

Any change in a variable or net can be detected using the @ event control, as in Verilog 2001. For more clarity, SystemVerilog also allows the @ event control to explicitly state any change, using the changed keyword:

@(myvar) // triggers on any change to myvar

@(changed myvar) // triggers on any change to myvar

If the expression evaluates to a result of more than one bit, a change on any of the bits of the result (including an x to z change) will trigger the event control. The @(changed expression) differs from @(expression) in that the changed keyword explicitly defines that the event control only triggers on a change of the result of the expression. In certain types of expressions, @(expression) may can trigger on changes to operands of the expression that do not affect the result.

per Stu's e-mail 28 Mar 2002

per Stu's e-mail 28 Mar 2002

SystemVerilog 3.0/draft 5 (3/29/02)

SystemVerilog allows assignment expressions to be used in an event control, e.g. @((a = b + c)). The event control is shall only be sensitive to changes in the result of the expression on the right-hand side of the assignment. It is shall not be sensitive to changes on the left-hand side expression.

# Section 9 State Machines

Editor's note: This section not yet indexed.

## 9.1 Introduction (informative)

Control logic, whether for a data path or an interface, is often specified as a Finite State Machine (FSM). Often this specification is in the form of a 'bubble' diagram, where circles represent states and arcs represent transitions. An alternative convention is to have vertical lines representing states and horizontal lines representing transitions. State machine capture tools often add hierarchy and concurrency to the basic FSM model.

Transitions are usually annotated with an input condition, for a synchronous FSM, or event, for an asynchronous one. In addition, an FSM may be active, i.e. it sets outputs. These outputs may be combinational functions of inputs (Mealy model) or just depend on the state (Moore model). These names have also been applied to procedural operations associated with a transition (Mealy) or a state (Moore).

To avoid timing hazards, inputs should not change at the same time as state. For an asynchronous FSM this normally means that input events should arrive well separated. For a synchronous FSM it means that other inputs should not change at the same time as the clock. Where two machines communicate, this in turn means that the outputs should not change until the inputs of both machines have been read. Nonblocking assignments are often used for this. Alternatively, delays can be put in the communication paths.

Verilog-2001 has no specific support for state machines. There are three modeling styles which are often used: case statements, named events, and implicit.

SystemVerilog adds several constructs specific to modeling state machines. These include named states and transitions, with dedicated syntax to distinguish them, and a semantics such that each statement is executed in a state or transition which can be determined by static analysis. The state is accessible to combinational logic.

The benefits of the SystemVerilog FSM constructs are readability for the user, including hierarchy and concurrency, ease of analysis for tools, and a better trade-off between debug and performance. The style should also support the software implementation of a state machine without any timing and without the overhead of extra events.

## 9.2 State machine constructs

The SystemVerilog state machine definition adds a new declaration type and two new statement types. The states are declared like an enumeration with a timing control. Note that S is used to represent both currentState and nextState:

```

state {S0, S1, S2} S @(posedge clock);

```

Editor's note: Per meeting 14, the keyword "state" needs to be changed to something else. It is a commonly used name in existing models.

SystemVerilog provides a transition statement, which can be used in a procedural block, such as an **always\_comb** block. As well as the state declaration, SystemVerilog uses the **transition** statement in procedural code The **transition** statement contains the individual state transitions shown by ->>:

```

transition (S)

S0: if (serial == 1) ->>S2;

S2: if (serial == 0) ->> S1; else ->> S0;

S1: ->> S0;

endtransition

```

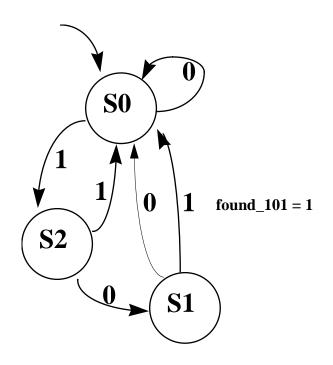

A complete example, referred to as the Wang and Edsall<sup>2</sup> example, is shown below. This Mealy style FSM has three states, a single input, and a single output. Its state structure is:

Figure 9-1—Simple state machine example

The three examples that follow illustrate some ways the state declaration and transitions can be used.

The following code illustrates how this state machine can be modeled using SystemVerilog. In this example the reset is synchronous, because the time control on the state declaration specifies transitions occur on the clock edge.

```

// SystemVerilog version of Wang & Edsall example, synchronous reset

module FSM1(output found_101, input serial, input clk, input reset);

state {S0, S1, S2} S @(posedge clk);

always_comb begin

found_101 = 0;

if (reset) ->> S.S0;

else transition (S)

S0: if (serial == 1) ->> S2;

S2: if (serial == 0) ->> S1; else ->> S0;

S1: ->> S0 if (serial == 1) found_101 = 1;

endtransition

end

endmodule

```

Note that the timing control in the example above can include a test for a condition, e.g. @(posedge clock iff !reset), showing that states change on the rising edge of the clock only if reset is 0.

Editor's note: poor usage of iff, as discussed in meeting 14.

<sup>&</sup>lt;sup>2</sup> T-H. Wang, T. Edsall "Practical FSM Analysis for Verilog", Proceedings, IVC 98, pp. 52-58.

The following example, the transition is instantaneous, because there is no timing control with the state declaration. Instead, the timing control is specified on the always procedure, with an asynchronous reset.

```

// SystemVerilog version of Wang & Edsall example, asynchronous reset

module FSM2(output logic found_101, input serial, input clock, input reset);

state {S0, S1, S2} S; // transition is instantaneous

always @(posedge clock or posedge reset) begin // asynchronous reset

if (reset) ->> S.S0;

else transition (S)

S0: if (serial == 1) ->> S2;

S2: if (serial == 0) ->> S1; else ->> S0;

S1: ->> S0;

endtransition

end

always_comb

if (S.S1 && serial == 1) found_101 = 1;

else found_101 = 0;

endmodule

```

In the next example, the transition is nonblocking, with a delay. The reset is asynchronous.

```

// SystemVerilog version of Wang & Edsall example, delayed transition

module FSM3(output logic found_101, input serial, input clock, input reset);

state {S0, S1, S2} S #lns; // transition is nonblocking with delay

always @(posedge clock or posedge reset) begin // asynchronous reset

if (reset) ->> S.S0;

else transition (S)

S0: if (serial == 1) ->> S2;

S2: if (serial == 0) ->> S1; else ->> S0;

S1: ->> S0;

endtransition

end

always_comb

if (S.S1 && serial == 1) found_101 = 1;

else found_101 = 0;

endmodule

```

# 9.3 State declarations

A SystemVerilog state declaration is syntactically based on an enumerated type:

```

[BNF excerpt to be inserted after BNF is approved]

```

Syntax 9-14—State declaration syntax

SystemVerilog 3.0/draft 5 (3/29/02)

Each state name shall be unique to the state declaration, so that if there are several state machines, the state names can overlap. Each state name can be preceded by a list of sub-states to represent a hierarchical state machine. The optional control expression is used to modify the nonblocking assignment to the state variable as described below.

The initial state is the first state listed. This is because the syntax <state variable> '=' <initial state> would be anomalous, since state variables cannot be assigned.

The state variable can be read as a string. for display purposes:

\$display (" state = %s", S);

The semantics differs both from an enumerated type and from a structure. Firstly the state name is not a constant but can be read as a variable that has a bit value which is 1 if the machine is in that state and a 0 if not, so it can be tested in conditions e.g. if(S.S2 | | S.S0).

Secondly the state variable cannot be assigned directly, but change to a new state is marked by a ->> operator. This updates the state machine to the new state as if an assignment were used. The optional timing control makes this assignment nonblocking with the specified delay. If more than one assignment is applied to happen at the same simulation time, the last one wins (there may be a race). This operator makes it easy to distinguish state changes from other assignments.

Editor's note: Per meetings 12-15, there are several open issues: - Need a method of specifying the state values. Syntax proposed is: state {S1=3'b001, S2=3'b010, S3=3'b100} S;

- Need to provide ability to do bit selects of state value, in order to model 1-hot encoding and such

- Need to describe and provide examples of synchronous and asynchronous resets

## 9.4 Transition statements

Syntax 9-15—State transition statement syntax

Each change of state shall be written as a transition\_to\_state. This can be unconditional, in which case the machine must be specified, or it can be in a transition statement, which also allows the transition to be named. Thus, each arc of the state diagram (represented by ->>) can be labeled (e.g. S0\_S2) as well as each node, as shown in the modified version of the Wang & Edsall example:

// SystemVerilog version of Wang & Edsall example with named transitions

```

module FSM5(output logic found_101, input serial, input clock, input reset);

state {S0, S1, S2} S @ (posedge clock);

always_comb begin

found_101 = 0;

if (reset) ->> S.S0;

else transition (S)

S0:if (serial == 1) S0_S2 ->>S2;

S2:if (serial == 0) S2_S1 ->> S1; else S2_S0 ->> S0;

S1: S1_S0 ->> S0 if (serial == 1) found_101 = 1;

endtransition

end

endmodule

```

The optional transition name is conceptually rather like an event name, but it differs in that it is not declared and must be unique in the state machine. A transition name may be used in an event expression elsewhere in the module e.g.  $@S0_S2$ . The timing of such a transition is the same as the event that triggered it e.g. @(posedge clk).

The state conditions are compared with the state variable, like the case conditions in a case statement. During execution, if the transition statement does not have a state matching the current state a run time warning occurs. If more than one state condition is specified, or the **default** keyword is used, the following transition cannot be given a name because there is more than one transition implied. The unconditional transition – >>A.B is an abbreviation for transition(A) default: ->>B; endtransition.

Transition names and entry and exit of states can be used like other event expressions to trigger other **always** blocks or for timing checks. The transition is written with the state machine name e.g.

@S.S0\_S2.

The change to a state can be written:

```

@(posedge S.S1)

```

and the change from a state can be written:

@(**negedge** S.S1)

Similarly any state change can be written:

@(S)

These state change event expressions trigger after the state has changed, i.e. later than the execution of the transition statement.

A simulator can check that the first transition to be executed is unconditional or contains a **default**, to model reset from an unreachable or unknown state.

The following example illustrates using **fork** and **join** with transitions on implicit named events, so that all transitions must have fired, in any order, to continue past the join.

```

initial begin

fork

@S.S0_S2;

@S.S2_S1;

@S.S2_S0;

join

end

```

SystemVerilog 3.0/draft 5 (3/29/02)

The state of state variables can be randomly initialized using an initial block with transitions determined by a random number.

## 9.5 Hierarchical and concurrent state machines

For large state machines it is convenient to structure the state space into states and sub-states. The states can be *or-states* which are comma separated, or *and-states*, e.g.

state {STA, {s1, s2, s3} STB, {{s4, s5, s6} c1 and {s7, s8} c2} STC} hsm1 @ clock;

This example can be illustrated as follows:

### Figure 9-2—Hierarchical state machine

Only one of a set of **or** states can be active at any time. But all **and** states are active or inactive simultaneously. Therefore, s4 and s7 can be active together.

Transitions are allowed from any state to any state, from any sub-state to any other state, and from one substate to another in the same state:

STA:->> STB; s1:if(input1) ->> STC; else ->> s2;

Other transitions to sub-states are not allowed. When a state contains or sub-states, entering the state implies entering the first sub-state. So ->> STB enters s1 as well. The truth value of the state name is the logical or of the truth values of the sub-states.

When a state contains **and** sub-states, entering the state implies entering all the sub-states, as shown by the two arrows in STC.

Two sub-states within and states can share a transition:

s5 and s7:T2 ->> s6 and s8;

The following example illustrates a more complex state machine of a two-player Reflex game<sup>3</sup>, with reset

logic and transition statements within a begin...end block.

```

// SystemVerilog description of two-player Reflex game. Note that this is

// an abstract model with events for input and enumeration for output

module REFLEX ( input event ready, stop, go, coin,

output enum {blue, yellow, red, green, flashing} light) ;

event timer;

always #10 ->timer;

state {

game_off,

{

{wait_ready, wait_go, wait_stop, done} player1 and

{idle, waiting} player2

} game_on

} game;

always begin: normal

// Either player may assert coin to start the game, status light turns blue

@(coin) transition (game) game_off: ->> game_on light = blue; endtransition

// When player 1 presses ready, the status light turns yellow

@(ready) transition (game)

wait_ready and idle: start->> wait_go and waiting light = yellow;

endtransition

// When player 2 presses go the status light turns green

fork : fork1

@(qo) disable fork1;

repeat ('L) @timer disable fork1; // if player 2 does not press go in time

@(stop) begin // stop before go

transition (game)

wait_go: ->> game_off light = flashing;

endtransition

disable normal;

end

join

transition (game)

wait_go and waiting: end2->> wait_stop and idle light = green;

endtransition

// Player 1 presses stop within L time units

fork : fork2

begin @(stop) transition (game)

wait_stop: ->> game_off light = red;

endtransition disable fork2; end

begin repeat ('L) @(timer) transition (game)

wait_stop: ->> game_off light = flashing;

endtransition disable fork2; end

join

```

<sup>&</sup>lt;sup>3</sup> "Hierarchical Finite State Machines with Multiple Concurrency Models", Alain Girault, Bilung Lee, Edward A Lee, IEEE Transactions on Computer Aided Design, Vol 18, No 6, June 1999, pp. 742.

```

end: normal

always @light $display("%t %s", $realtime, light);

endmodule

```

# Section 10 Processes

## 10.1 Introduction (informative)

Verilog-2001 has **always** and **initial** blocks which define static processes.

Verilog 2001 has a continuous assignment to describe combinational logic. However, it is missing a case statement for multiplexers and there is no name for the driving value if the wire has multiple drivers.